Diagramas de Sistemas de Controle de Elo CC¶

A terminologia técnica adotada nos diagramas dos Sistemas de Controle de Elo CC é detalhada na seção Terminologia Técnica dos Modelos Predefinidos de Conversor LCC.

Diagramas do Modelo 01 de Controle de Conversor CA-CC¶

(*) Clique na imagem para visualizar os detalhes da figura

Diagrama de Blocos do CCA, VCO, CEC e Controle de \(U_{min}\) e \(A_{min}/ \gamma_{min}\)¶

(*) Clique na imagem para visualizar os detalhes da figura

Diagrama de Blocos do VDCOL (Voltage Dependent Current Order Limiter)¶

(*) Clique na imagem para visualizar os detalhes da figura

Diagrama de Blocos do Controle de Potência (“master control”)¶

(*) Clique na imagem para visualizar os detalhes da figura

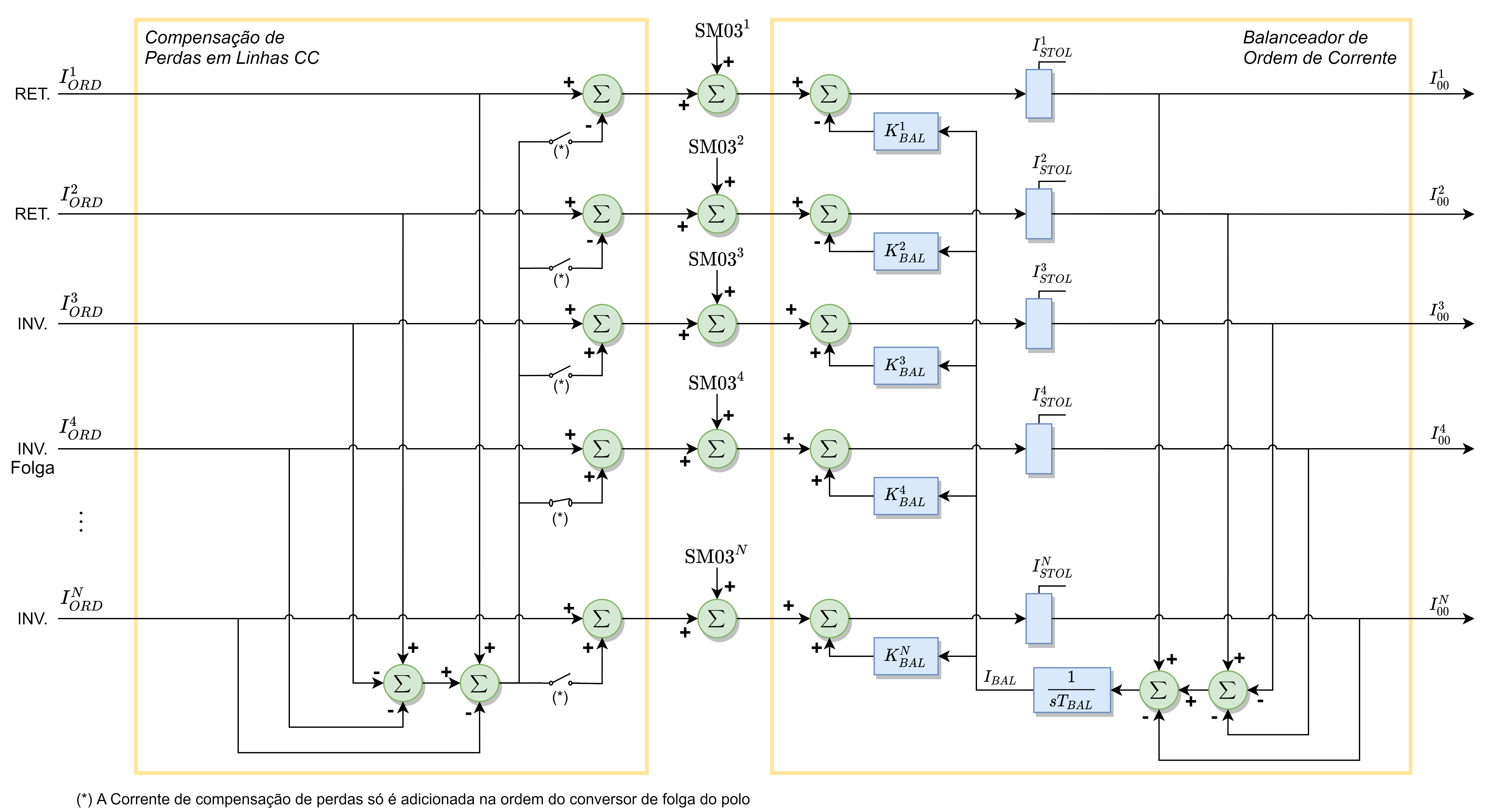

Diagrama de Blocos do Controle de Elo CC¶

(*) Clique na imagem para visualizar os detalhes da figura

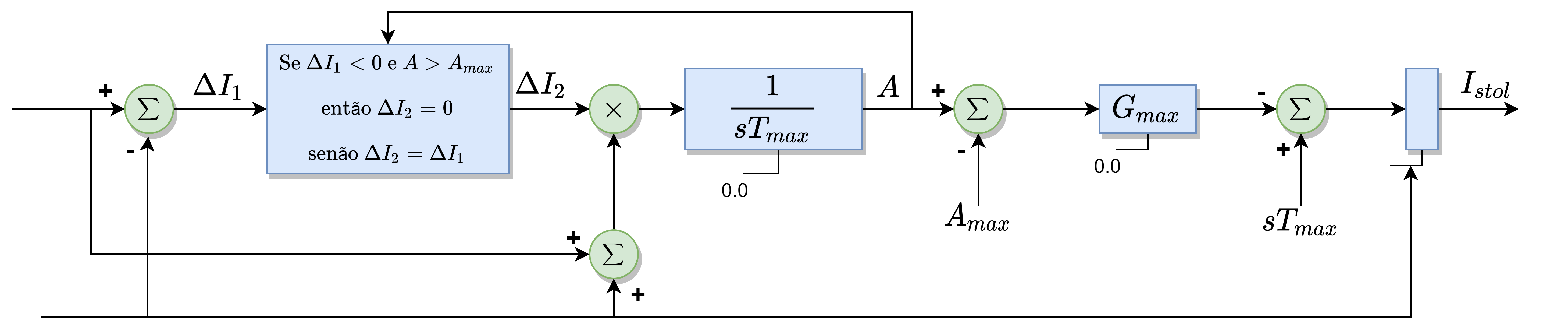

Diagrama de Blocos do Controle de Sobrecarga de Corrente¶

(*) Clique na imagem para visualizar os detalhes da figura

Diagramas do Modelo 03 de Controle de Conversor CA-CC¶

(*) Clique na imagem para visualizar os detalhes da figura

Diagrama de Blocos do CCA, VCO, CEC e Controle de \(U_{min}\) e \(A_{min}/ \gamma_{min}\)¶

(*) Clique na imagem para visualizar os detalhes da figura

Diagrama de Blocos do RIAC (Rectifier Integrator Alpha Clamp)¶

(*) Clique na imagem para visualizar os detalhes da figura

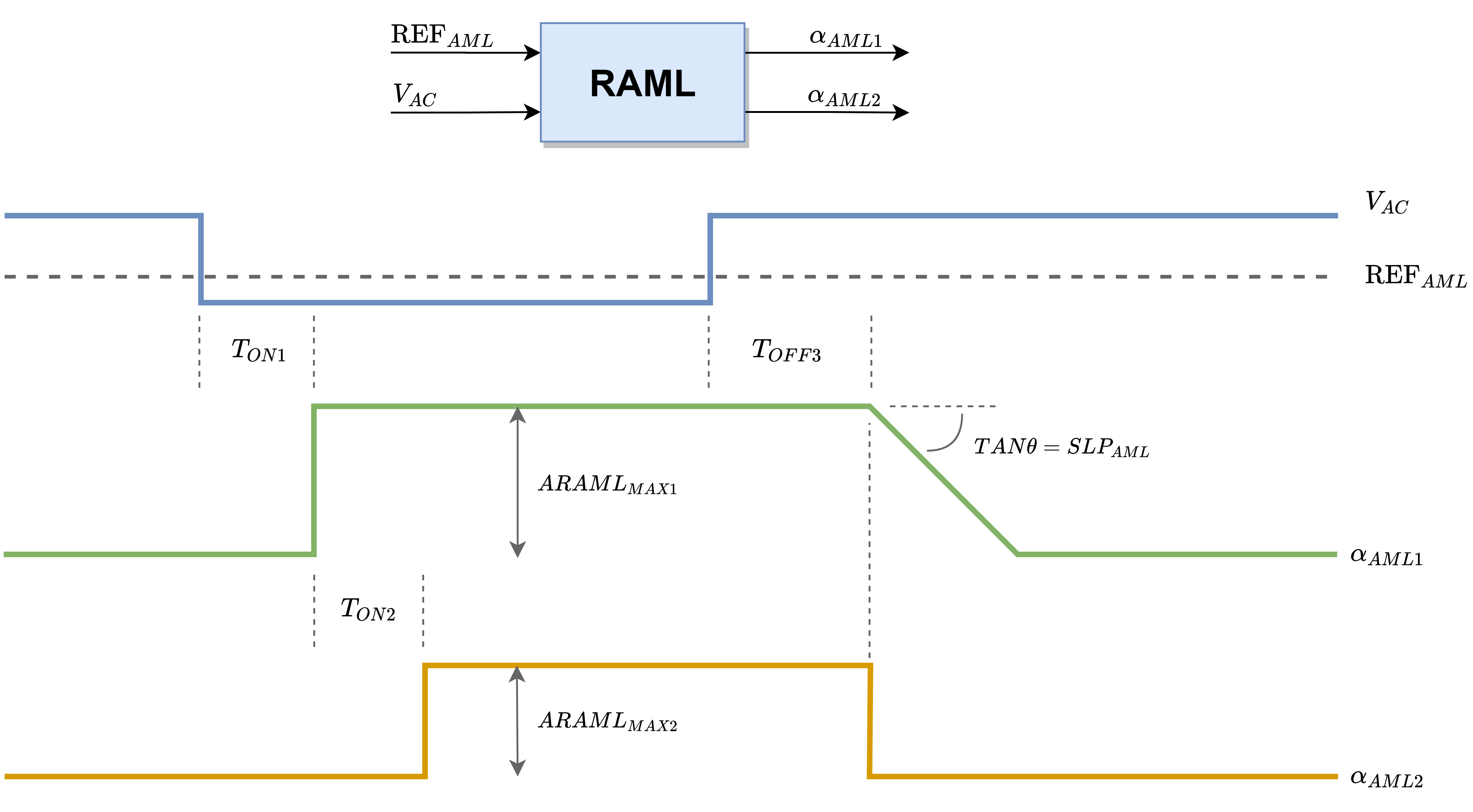

Descrição do Comportamento do Bloco RAML (Rectifier Alpha Minimum Limiter)¶

(*) Clique na imagem para visualizar os detalhes da figura

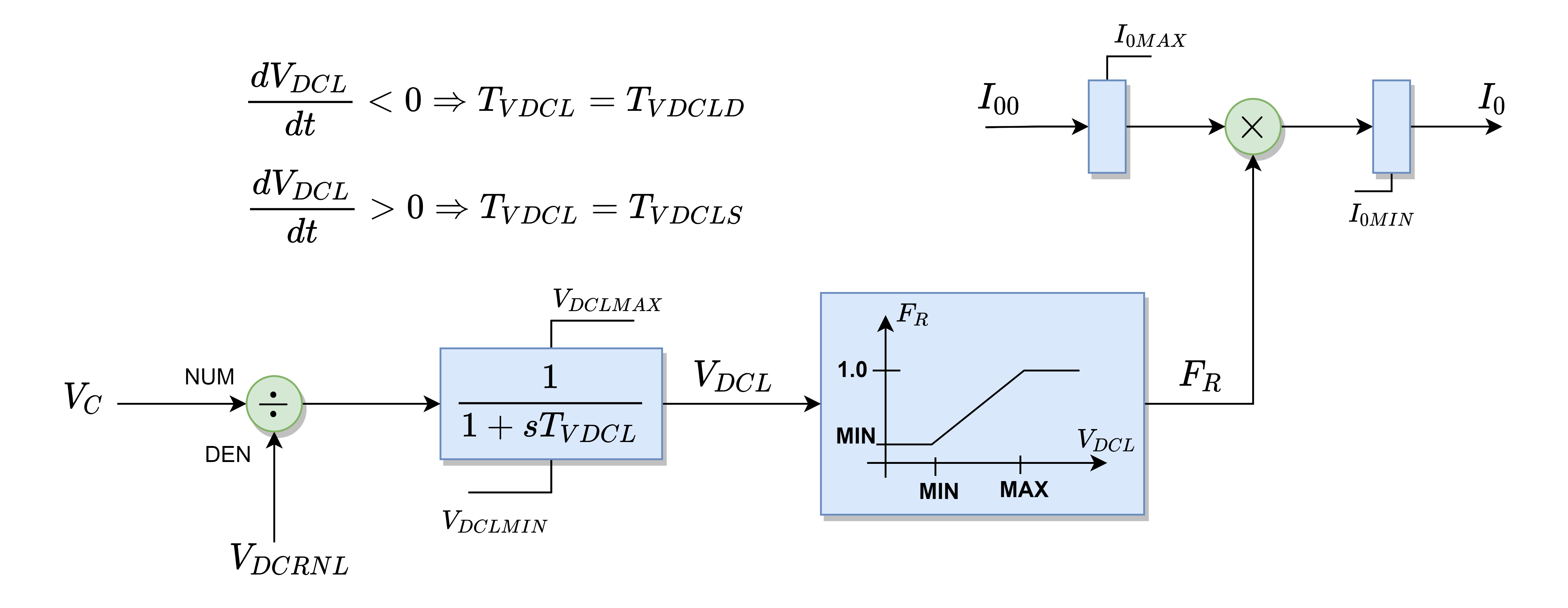

Diagrama de Blocos do VDCOL (Voltage Dependent Current Order Limiter)¶

(*) Clique na imagem para visualizar os detalhes da figura

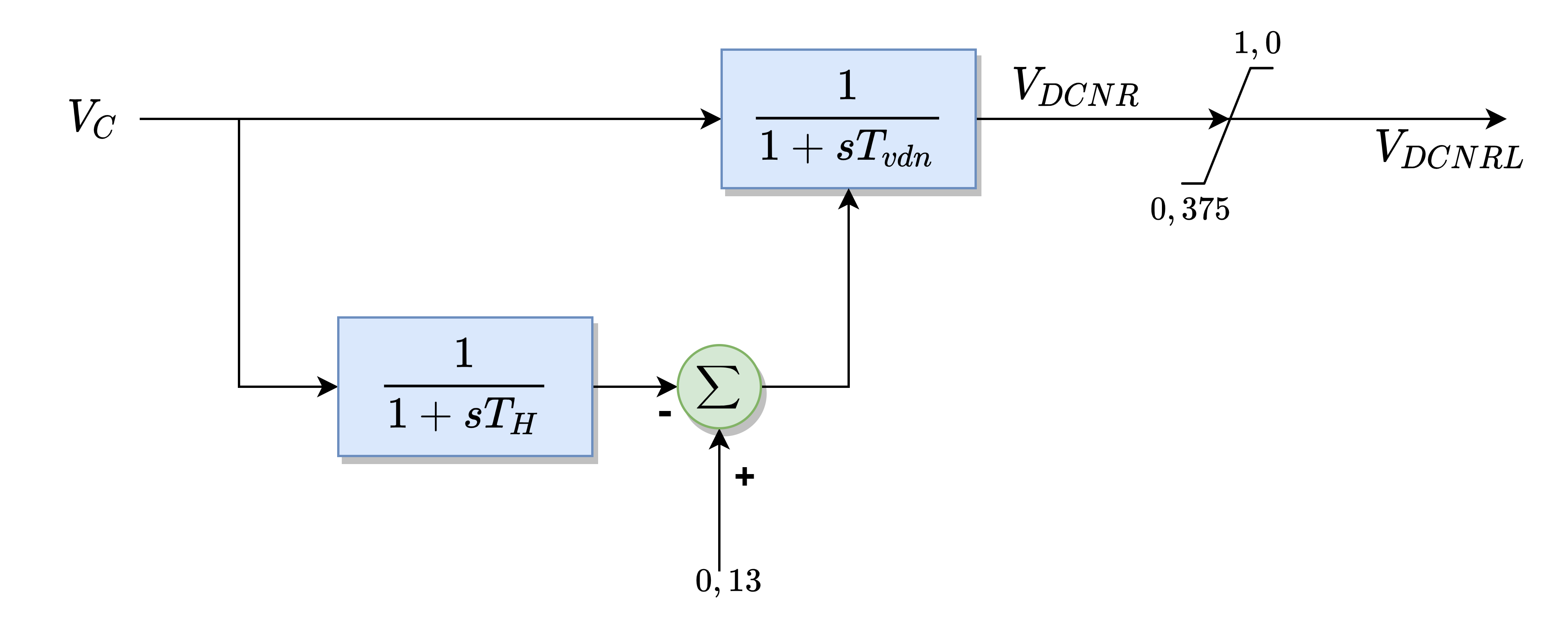

O circuito abaixo mostra o cálculo do sinal VDCRNL a ser usado na normalização do VDCOL (para o modelo 1 é usado um valor constante igual ao valor inicial da tensão do conversor \(V_c\)). O bloco com constante \(T_H\) gera um sinal que quando for menor que 0,13 sinaliza o congelamento do bloco com constante \(T_{vdn}\). A constante \(T_H\) possui um valor de 0,004 s quando \(V_c\) for decrescente e 0,114 quando \(V_c\) for crescente.

Diagrama de Blocos do Controle de Potência (“master control”)¶

Em relação ao modelo 1 foram acrescentados o limite \(V_{DCmin}\), o filtro com constante de tempo \(T_{mst}\) na ordem de potência \(P_{set}\), a temporização do ciclo de cálculo do controle de potência (S/H) e o atraso de telecomunicação. O valor CURH é atualizado a cada THOLDM segundos.

O atraso de telecomunicação é diferente para os terminais retificador e inversor, pois no caso de diminuição da ordem esta só deve ser enviada ao retificador depois de confirmado o recebimento pelo terminal inversor.

Controle de potência - Diagrama principal:

Atraso de telecomunicação para retificador:

Atraso de telecomunicação para inversor:

Diagrama de Blocos do Controle de Elo CC¶

(*) Clique na imagem para visualizar os detalhes da figura

Diagrama de Blocos do Controle de Sobrecarga de Corrente¶

(*) Clique na imagem para visualizar os detalhes da figura